# Lecture Notes in Computer Science

4006

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

**David Hutchison**

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Luís Miguel Pinho Michael González Harbour (Eds.)

# Reliable Software Technologies – Ada-Europe 2006

11th Ada-Europe International Conference on Reliable Software Technologies Porto, Portugal, June 5-9, 2006 Proceedings

#### Volume Editors

Luís Miguel Pinho Polytechnic Institute of Porto School of Engineering (ISEP)

Rua Dr. António Bernardino de Almeida, 431, 4200-072 Porto, Portugal

E-mail: lpinho@dei.isep.ipp.pt

Michael González Harbour Universidad de Cantabria Departamento de Electrónica y Computadores Avda. de los Castros s/n, 39005-Santander, Spain E-mail: mgh@unican.es

Library of Congress Control Number: 2006926424

CR Subject Classification (1998): D.2, D.1.2-5, D.3, C.2.4, C.3, K.6

LNCS Sublibrary: SL 2 – Programming and Software Engineering

ISSN 0302-9743

ISBN-10 3-540-34663-5 Springer Berlin Heidelberg New York ISBN-13 978-3-540-34663-0 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2006 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 11767077 06/3142 5 4 3 2 1 0

#### **Preface**

The 11th International Conference on Reliable Software Technologies, Ada-Europe 2006, took place in Porto, Portugal, June 5-9, 2006. It was as usual sponsored by Ada-Europe, the European federation of national Ada societies, in cooperation with ACM SIGAda. It was organized by members of the School of Engineering of the Polytechnic Institute of Porto, in collaboration with several colleagues from different institutions in Europe.

Following the usual style, the conference included a three-day technical program, during which the papers contained in these proceedings were presented, bracketed by two tutorial days where attendants had the opportunity to catch up on a variety of topics related to the field, at both introductory and advanced levels. Continuing the success achieved in the previous year, the technical program also included an industrial track, with contributions illustrating challenges faced and solutions encountered by industrialists from both sides of the Atlantic. Furthermore, the conference was accompanied by an exhibition where vendors presented their products for supporting reliable-software development.

The conference presented four distinguished speakers, who delivered state-ofthe-art information on topics of great importance, both for the present and the future of software engineering:

- Correctness by Construction: Putting Engineering into Software by Rod Chapman (Praxis HIS, UK)

- Empirical Software Risk Assessment Using Fault Injection by Henrique Madeira (University of Coimbra, Portugal)

- Model-Driven Technologies in Safe-Aware Software Applications by Miguel Angel de Miguel (Technical University of Madrid, Spain)

- I Have a Dream: ICT Problems We All Face by John L. Hill (Sun Microsystems, USA)

We would like to express our sincere gratitude to these distinguished speakers, well known to the community, for sharing their insights with the conference participants.

A large number of regular papers were submitted, from as many as 23 different countries. The Program Committee worked hard to review them, and the selection process proved to be difficult, since many papers had received excellent reviews. Finally, the Program Committee selected 19 papers for the conference. The industrial track of the conference also received valuable contributions from industrialists, and the Industrial Committee finally selected 9 of them for the conference. The final result was a truly international program with contributions from Australia, Austria, Canada, China, France, Germany, Iran, Italy, Japan, Portugal, Spain, the UK, and the USA, covering a broad range of topics: real-time systems, static analysis, verification, applications, reliability, industrial experience, compilers and distributed systems.

The conference also included an interesting selection of tutorials, featuring international experts who presented introductory and advanced material in the domain of the conference:

- Verification and validation for reliable software systems, William Bail

- The Ada 2005 Standard Container Library, Matthew Heaney

- Developing Web-Aware Applications in Ada with AWS, Jean-Pierre Rosen

- SAE Architecture Analysis and Design Language, Joyce L. Tokar

- Model-Driven Development with the Unified Modeling Language (UML)  $2.0^{\rm TM}$  and Ada, Colin~Coates

- Distribution in Ada 95 with PolyORB, A Schizophrenic Middleware, Jérôme Hugues

- Requirements Management for Dependable Systems, William Bail

- Real-Time Java for Ada Programmers, Benjamin M. Brosgol

We would like to express our appreciation to these experts, for the work on preparing and presenting this material in the conference.

Many people contributed to the success of the conference. The Program and Industrial Committees, made up of international experts in the area of reliable software technologies, spent long hours carefully reviewing all the papers, presentations and tutorial proposals submitted to the conference. A subcommittee comprising Dirk Craeynest, Michael González Harbour, Laurent Pautet, Luís Miguel Pinho, Erhard Plöedereder, Jorge Real, and Tullio Vardanega met in Porto to make the final program selection. Various Program Committee members were assigned to shepherd some of the papers. We are grateful to all those who contributed to the technical program of the conference.

We would also like to thank the members of the Organizing Committee, for their valuable effort in taking care of all the bits and pieces that must fit together for a smooth run of the conference. We would like to thank Peter Dencker for the effort in the preparation of the industrial track, to Jorge Real for the attractive tutorial program and to José Ruiz for preparing the appealing exhibition of the conference. Also to Dirk Craeynest, who worked very hard to make the conference prominently visible, and to all the members of the Ada-Europe board for helping with the intricate details of the organization. A special thanks to Sandra Almeida, who took care of all details of the local organization.

Finally, we would like to express our appreciation to the authors of the contributions submitted to the conference, and to all the participants who helped in achieving the goal of the conference: providing a forum for researchers and practitioners for the exchange of information and ideas about reliable software technologies. We hope they all enjoyed the program as well as the social events of the 11<sup>th</sup> International Conference on Reliable Software Technologies.

# Organization

#### Conference Chair

Luís Miguel Pinho, Polytechnic Institute of Porto, Portugal

#### **Program Co-chairs**

Luís Miguel Pinho, Polytechnic Institute of Porto, Portugal Michael González Harbour, Universidad de Cantabria, Spain

#### **Industrial Committee Co-chairs**

Peter Dencker, Aonix GmbH, Germany Michael González Harbour, Universidad de Cantabria, Spain

#### **Tutorial Chair**

Jorge Real, Universidad Politécnica de Valencia, Spain

#### **Exhibition Chair**

José Ruiz, AdaCore, France

#### **Publicity Chair**

Dirk Craeynest, Aubay Belgium and K.U. Leuven, Belgium

#### Local Chair

Sandra Almeida, Polytechnic Institute of Porto, Portugal

#### Ada-Europe Conference Liaison

Laurent Pautet, Telecom Paris, France

# Program Committee

Alejandro Alonso, Universidad Politécnica de Madrid, Spain Lars Asplund, Mälardalens Högskola, Sweden Janet Barnes, Praxis High Integrity Systems, UK Guillem Bernat, University of York, UK Johann Blieberger, Technische Universität Wien, Austria

#### VIII Organization

Ben Brosgol, AdaCore, USA Bernd Burgstaller, University of Sydney, Australia Alan Burns, University of York, UK

Dirk Craeynest, Aubay Belgium and K.U. Leuven, Belgium

Alfons Crespo, Universidad Politécnica de Valencia, Spain

Raymond Devillers, Université Libre de Bruxelles, Belgium

Michael González Harbour, Universidad de Cantabria, Spain

José Javier Gutiérrez, Universidad de Cantabria, Spain

Andrew Hately, Eurocontrol CRDS, Hungary

Günter Hommel, Technische Universität Berlin, Germany Hubert Keller, Institut für Angewandte Informatik, Germany

Yvon Kermarrec, ENST Bretagne, France

Jörg Kienzle, McGill University, Canada

Fabrice Kordon, Université Pierre and Marie Curie, France

Albert Llamosi, Universitat de les Illes Balears, Spain

Franco Mazzanti, ISTI-CNR Pisa, Italy

John McCormick, University of Northern Iowa, USA

Stephen Michell, Maurya Software, Canada

Javier Miranda, Universidad Las Palmas de Gran Canaria, Spain

Laurent Pautet, Telecom Paris, France

Luís Miguel Pinho, Polytechnic Institute of Porto, Portugal

Erhard Plödereder, Universität Stuttgart, Germany

Juan A. de la Puente, Universidad Politécnica de Madrid, Spain

Jorge Real, Universidad Politécnica de Valencia, Spain

Alexander Romanovsky, University of Newcastle upon Tyne, UK

Jean-Pierre Rosen, Adalog, France

José Ruiz, AdaCore, France

Edmond Schonberg, New York University and AdaCore, USA

Joyce Tokar, Pyrrhus Software, USA

Tullio Vardanega, Università di Padova, Italy

Andy Wellings, University of York, UK

Jürgen Winkler, Friedrich-Schiller-Universität, Germany

#### Reviewers

Gaetan Allaert

Alejandro Alonso

Mrio Amado Alves

Wolfram Amme

Lars Asplund

Ricardo Barbosa

Janet Barnes

Johann Blieberger

Maarten Boasson

Ben Brosgol

Bernd Burgstaller

Alan Burns

Dirk Craeynest

Alfons Crespo

Garreg Lewis Dawe

Raymond Devillers

Michael González Harbour

José Javier Gutiérrez

Andrew Hately

Günter Hommel

Stefan Kauer

Hubert Keller

Yvon Kermarrec

Jörg Kienzle

Fabrice Kordon

Albert Llamosi

Kristina Lundqvist

Franco Mazzanti

John McCormick

Stephen Michell

Javier Miranda

Gustaf Naeser

Martin Ouimet

Laurent Pautet

Luís Miguel Pinho Erhard Plödereder Juan A. de la Puente

Jorge Real

Alexander Romanovsky

Philippe Rose Jean-Pierre Rosen

José Ruiz

Edmond Schonberg

Joyce Tokar Tullio Vardanega Andy Wellings Jürgen Winkler

# **Table of Contents**

# Real-Time Systems

| Hierarchical Scheduling with Ada 2005  José A. Pulido, Santiago Urueña, Juan Zamorano, Tullio Vardanega,  Juan A. de la Puente                                          | 1   |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| A Comparison of Ada and Real-Time Java $^{\mathrm{TM}}$ for Safety-Critical Applications<br>Benjamin M. Brosgol, Andy Wellings                                          | 13  |  |  |  |

| POSIX Trace Based Behavioural Reflection Filipe Valpereiro, Luís Miguel Pinho                                                                                           | 27  |  |  |  |

| Static Analysis                                                                                                                                                         |     |  |  |  |

| Static Detection of Access Anomalies in Ada95 Bernd Burgstaller, Johann Blieberger, Robert Mittermayr                                                                   | 40  |  |  |  |

| One Million (LOC) and Counting: Static Analysis for Errors and Vulnerabilities in the Linux Kernel Source Code  Peter T. Breuer, Simon Pickin                           | 56  |  |  |  |

| Bauhaus – A Tool Suite for Program Analysis and Reverse Engineering  Aoun Raza, Gunther Vogel, Erhard Plödereder                                                        | 71  |  |  |  |

| Verification                                                                                                                                                            |     |  |  |  |

| SPARK Annotations Within Executable UML  Damian Curtis                                                                                                                  | 83  |  |  |  |

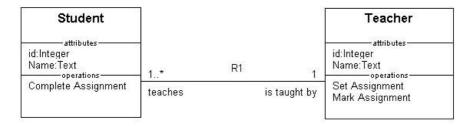

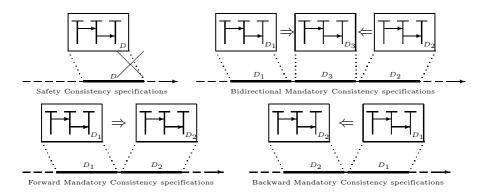

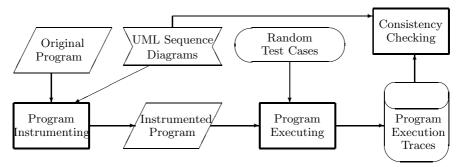

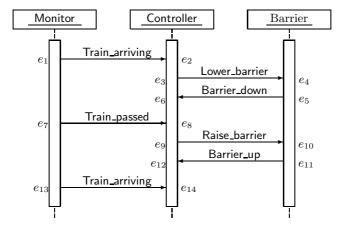

| Runtime Verification of Java Programs for Scenario-Based Specifications  Xuandong Li, Linzhang Wang, Xiaokang Qiu, Bin Lei,  Jiesong Yuan, Jianhua Zhao, Guoliang Zheng |     |  |  |  |

| Applications                                                                                                                                                            |     |  |  |  |

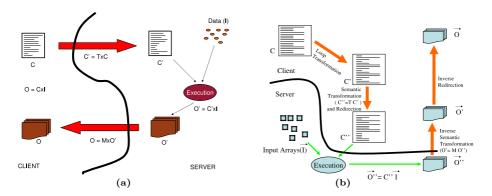

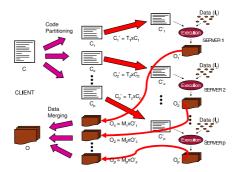

| Secure Execution of Computations in Untrusted Hosts S.H.K. Narayanan, M.T. Kandemir, R.R. Brooks, I. Kolcu                                                              | 106 |  |  |  |

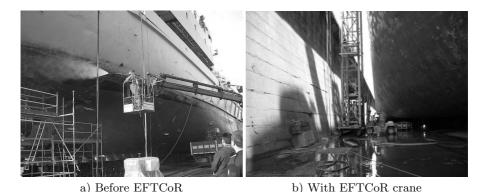

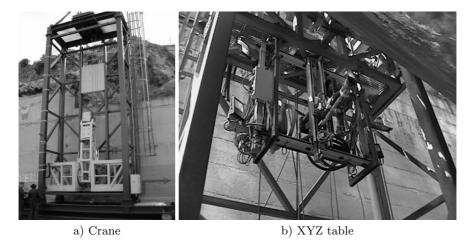

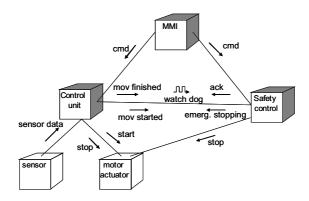

| A Systematic Approach to Developing Safe Tele-operated Robots<br>Diego Alonso, Pedro Sánchez, Bárbara Álvarez, Juan A. Pastor                                           |     |  |  |  |

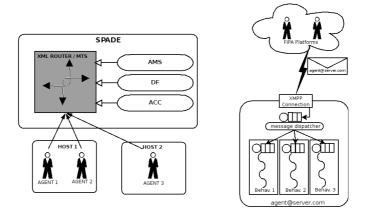

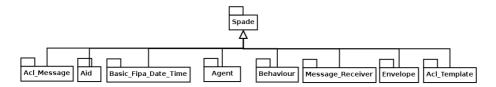

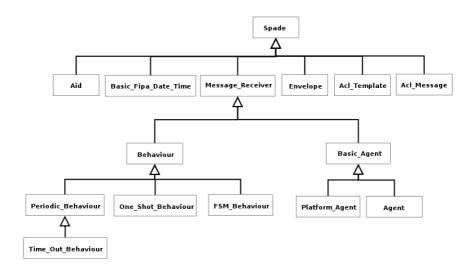

| Towards Developing Multi-agent Systems in Ada<br>G. Aranda, J. Palanca, A. Espinosa, A. Terrasa,<br>A. García-Fornes                                                                                                 | 131        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Reliability                                                                                                                                                                                                          |            |

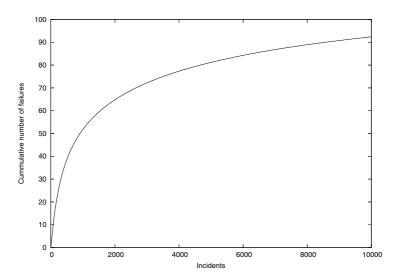

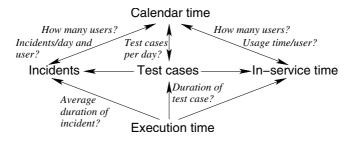

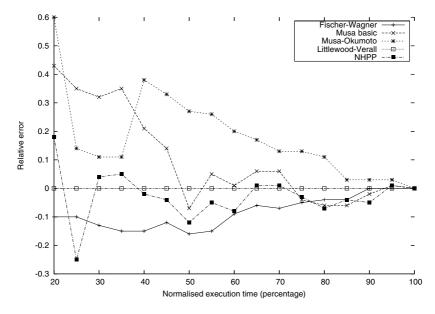

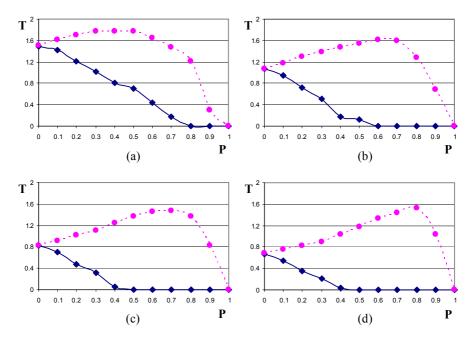

| A Software Reliability Model Based on a Geometric Sequence of Failure Rates                                                                                                                                          | 1.49       |

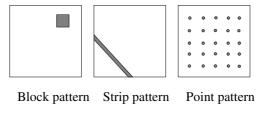

| Stefan Wagner, Helmut Fischer  Adaptive Random Testing Through Iterative Partitioning  T.Y. Chen, De Hao Huang, Zhi Quan Zhou                                                                                        | 143<br>155 |

| Run-Time Detection of Tasking Deadlocks in Real-Time Systems with the Ada 95 Annex of Real-Time Systems  Jingde Cheng                                                                                                | 167        |

| Compilers                                                                                                                                                                                                            |            |

| Abstract Interface Types in GNAT: Conversions, Discriminants, and C++  Javier Miranda, Edmond Schonberg                                                                                                              | 179        |

| Using Mathematics to Improve Ada Compiled Code  Ward Douglas Maurer                                                                                                                                                  | 191        |

| Distributed Systems                                                                                                                                                                                                  |            |

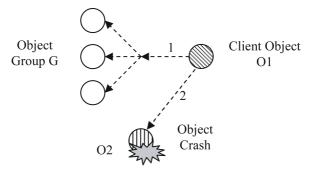

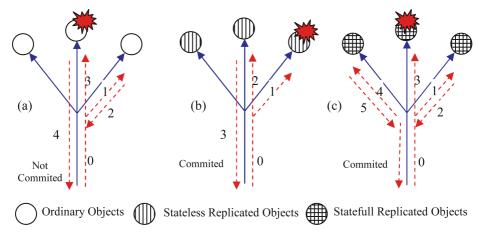

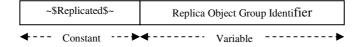

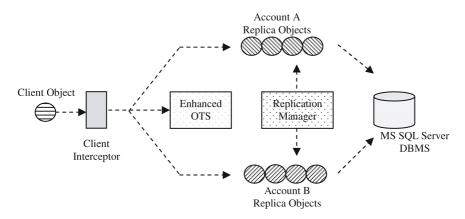

| Replication-Aware Transactions: How to Roll a Transaction over Failures  Mohsen Sharifi, Hadi Salimi                                                                                                                 | 203        |

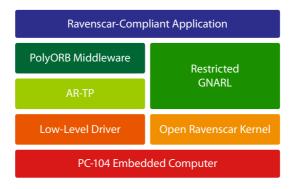

| The Arbitrated Real-Time Protocol (AR-TP): A Ravenscar Compliant Communication Protocol for High-Integrity Distributed Systems  Santiago Urueña, Juan Zamorano, Daniel Berjón, José A. Pulido,  Juan A. de la Puente | 215        |

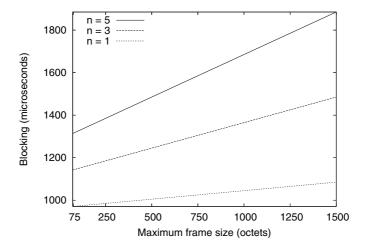

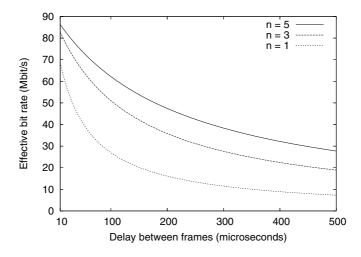

| Interchangeable Scheduling Policies in Real-Time Middleware for<br>Distribution                                                                                                                                      |            |

| Juan López Campos, J. Javier Gutiérrez,  Michael González Harbour                                                                                                                                                    | 227        |

| Author Index                                                                                                                                                                                                         | 241        |

# Hierarchical Scheduling with Ada 2005\*

José A. Pulido<sup>1</sup>, Santiago Urueña<sup>1</sup>, Juan Zamorano<sup>1</sup>, Tullio Vardanega<sup>2</sup>, and Juan A. de la Puente<sup>1</sup>

Departamento de Ingeniería de Sistemas Telemáticos (DIT) Universidad Politécnica de Madrid (UPM), E28040 Madrid, Spain {pulido, suruena, jzamorano, jpuente}@dit.upm.es

Dipartimento di Matematica Pura ed Applicata Università di Padova, I35131 Padova, Italy tullio.vardanega@math.unipd.it

Abstract. Hierarchical scheduling is a basic technique to achieve temporal isolation between applications in high-integrity systems when an integrated approach is opted for over traditional federation. While comparatively heavyweight approaches to hierarchical scheduling have been prevailing until now, the new scheduling features of Ada 2005 enable lighter-weight techniques to be used. This will expectedly result in increasing the efficiency and flexibility of hierarchical scheduling, thus enabling new ways to developing critical applications in Ada. The paper explores the new opportunities opened by Ada 2005 and proposes some concrete techniques for implementing hierarchical scheduling in the new version of the language.

#### 1 Introduction

High-integrity systems (HIS) are applications with stringent safety or security requirements, in which a failure can have unacceptable consequences [1]. Such systems are usually required to exhibit a fully predictable behaviour, to which end comprehensive verification and validation (V&V) processes must be deployed. The particular approach and techniques that must be used in different applications are often described in domain-specific certification standards, such as DO-178B (civil avionics), IEC 601-4 (medical systems), IEC 880 (nuclear power plants), EN 50128 (European railways), etc. These standards define different criticality levels (CL), as well as the V&V requirements that must be met by an application candidate for certification at a given level. The applications in turn must be classified into the different criticality levels, depending on the severity of the consequences of a potential failure.

Complex systems are often composed of several applications that may be classified at differing criticality levels. A common requirement for this kind of systems is to isolate the most critical applications from the less critical ones, so that a failure in the latter does not compromise the behaviour of the vital parts

<sup>\*</sup> This work has been supported by the Spanish Ministry of Education, project no. TIC2002-04123-C03-01.

L.M. Pinho and M. González Harbour (Eds.): Ada-Europe 2006, LNCS 4006, pp. 1–12, 2006. © Springer-Verlag Berlin Heidelberg 2006

of the system. Isolation has often been achieved by building systems according to a federated approach, i.e. by allocating different applications to different computer platforms. However, the processing power of current processors eases the adoption of more efficient, integrated architectures in which several applications, possibly with different criticality levels, share a common computer platform. Under this approach, alternate architectural mechanisms must be sought to provide the required degree of isolation among applications. The computer platform is divided into a number of logical partitions, each of which is allocated a share of the available computer resources, including processor time and memory space. Each application runs on one of the partitions, and partitions are isolated from each other both in the temporal and spatial domains:

- Temporal isolation means that a partition cannot use processor time allocated to other partitions as long as the applications running on them are ready to execute. Temporal isolation ensures that high criticality applications are not prevented from meeting their temporal requirements by the misbehaviour of lower-criticality applications. Indeed, the converse is also true, although not that useful in practical situations. Since high criticality applications are usually subject to strict validation and verification procedures, in most cases it can be safely assumed that they do not incur overruns.

- Spatial isolation means that a partition cannot access memory outside its allocated storage space. Therefore, high criticality applications can safely assume that low criticality applications will not change any data in their memory space by the effect of misbehaviour.

Temporal and spatial isolation collectively enable high criticality applications to run in the same computer platform as other, lower criticality, applications whilst preserving their integrity in the face of faults in the latter, which thus need not be developed under the same stringent validation and verification processes.

This paper is focused on temporal isolation, for which a new architectural approach making use of the new Ada 2005 scheduling features is presented. The concept of hierarchical scheduling as a general approach to temporal isolation is introduced and discussed in section 2. Section 3 introduces the proposed architecture and shows how it can be implemented using the Ada 2005 scheduling model. Temporal analysis and implementation issues are discussed in section 4.1. Finally, some conclusions are presented in section 5.

### 2 Hierarchical Scheduling

#### 2.1 Temporal Isolation

Depending on the granularity of partitioning, a partition contains a number of execution tasks performing functions with the same criticality level. Appropriate scheduling and temporal analysis methods (see e.g. [2]) can be used at design time to ensure that threads running in a partition will not "steal" (by overrun) processor time budgeted to other partitions. However, since temporal analysis

is based on design assumptions that may be violated at run time, some kind of run-time mechanisms (e.g. based on clocks and timers) must be used to warrant isolation in the face of a possible misbehaviour of the application threads.

#### 2.2 Hierarchical Scheduling

Hierarchical scheduling is a technique that can be used to implement isolation between logical partitions. The main idea behind it is to use two kinds of schedulers on the same computer platform:

- A global scheduler, which allocates the processor to a partition in accord with a global scheduling policy. The partition that has the processor at a given instant is called the active partition.

- A local scheduler, which is used to decide which task among those that are ready to run within the active partition executes first, following a local scheduling policy.

Several schemes are possible for global and local scheduling policies, including static scheduling, time slicing, dynamic priorities and fixed priorities. Some architectural patterns that have been proposed in this framework are fully partitioned architectures and server-based architectures. The main properties of these architectures are described in the next paragraphs.

#### 2.3 Fully Partitioned Architecture

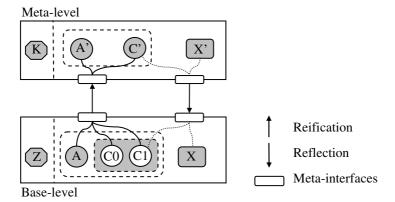

This architectural pattern entails using a completely separated global scheduler, and as many local schedulers as logical partitions. When the global scheduler dispatches a partition for execution, it yields control to the local scheduler in that partition, which in turn dispatches ready tasks within the partition according to the local scheduling policy. With this approach, different partitions may have different local scheduling policies.

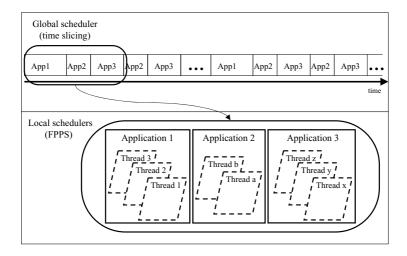

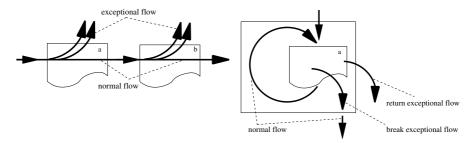

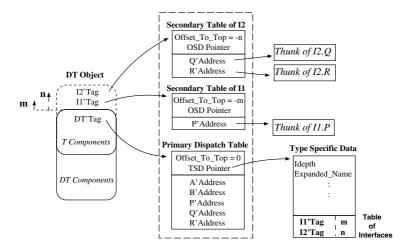

A well-known example of this model is the ARINC 653 standard [3] for avionics systems (figure 1). The ARINC global scheduler is a variant of a static cyclic executive, while the local schedulers are priority-based. Some proposals to build systems in Ada based on this architecture have been presented in recent years [4, 5].

The main advantage of this approach is the guarantee of timeliness and predictability. However, the approach also suffers from the same drawbacks as other static scheduling methods, for it is rigid and inflexible. It is in fact difficult to modify the configuration of a system by adding or changing partitions. Moreover, the communication scheme is very rigid and the problem of allocating sporadic tasks is hard. All in all, this model approach scales poorly to increasing levels of architectural partitioning.

Other approaches within the same overall strategy are obviously possible, however, under the fully partitioned architecture. For example, fixed priorities could be employed for global scheduling, or else dynamic priorities could be used at the local level. The strict separation between schedulers at different partitions

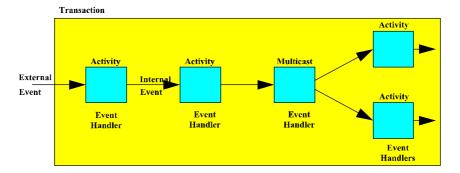

Fig. 1. Fully partitioned architecture

and the global scheduler enables a rich variety of scheduling methods to be accommodated under this architecture, although practical considerations and the apparent need for further research on temporal analysis methods for partitioned architectures may impair the development of mixed scheduling methods.

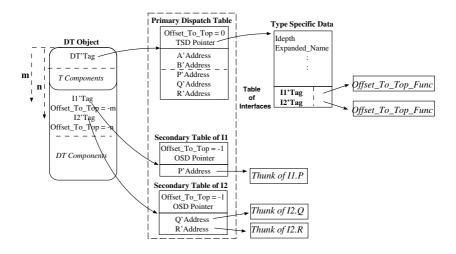

#### 2.4 Served-Based Architecture

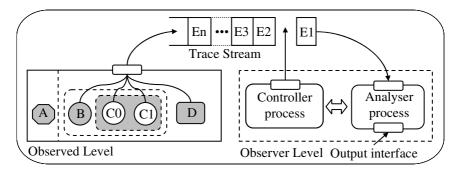

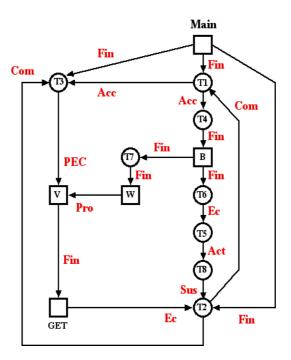

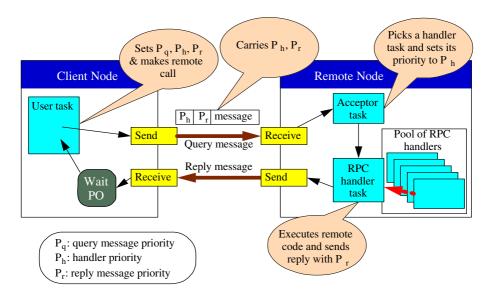

The server-based architecture goes one step further, adding flexibility to the fully static partitioned model while preserving a high degree of robustness and staying comparatively simple to implement. In this architecture the global scheduler is supplemented by a set of servers (cf. figure 2), which are specialized containers for executing application tasks. Servers have a capacity of processor time, which can be replenished at different times. When a server is dispatched for execution, it in turn dispatches the tasks it serves according to the local scheduling policy as long as it retains some residual processing time from its original capacity. When the server capacity is exhausted, it suspends its execution until the capacity is replenished.

An example of this approach is the FIRST architecture [6], one variant of which uses fixed-priority pre-emptive scheduling (FPPS) at the global level, and different kinds of servers to execute the application tasks:

- A periodic server [7] is released with a fixed period. As long as there are any tasks ready to run, they are executed until the server capacity is exhausted.

If the tasks complete and there is some capacity available, the server remains idle in case a task is released that can use some of the remaining capacity.

The server capacity is replenished at the beginning of the next period.

- A deferrable server [8] is similar to a periodic server, except that it suspends its execution if there are no ready tasks to be run. Its capacity is replenished

Fig. 2. Server-based architecture

at the beginning of the next period, independently of whether it has been consumed or not.

- A sporadic server [9] is replenished only after its capacity has been exhausted. The amount of capacity to be replenished and the time to do it depend on the particular way that the tasks are scheduled.

Unlike the fully partitioned architecture, this priority-based method improves the flexibility of the system substantially, while also keeping a reasonable degree of timeliness and predictability. An exhaustive discussion of the schedulability analysis issues arising from the approach has been made in [6]. One distinct conclusion of the cited work is that periodic servers are best equipped to warrant the deadline of hard real-time tasks, while also noting the current difficulty of choosing optimal parameters for the servers.

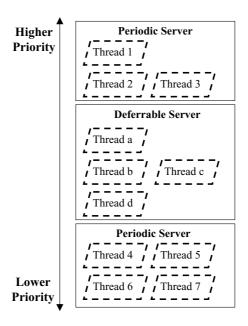

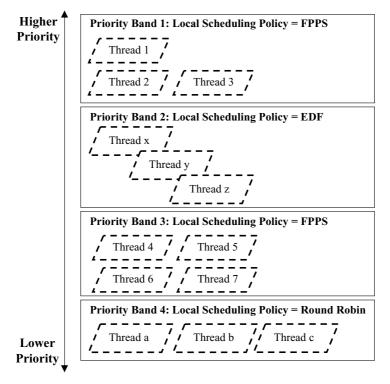

## 3 An Architecture Based on Priority Bands

#### 3.1 General Approach

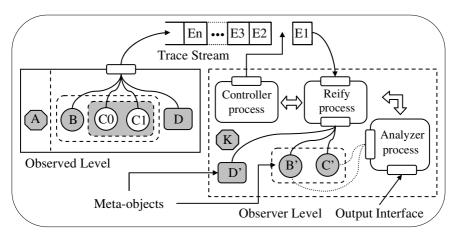

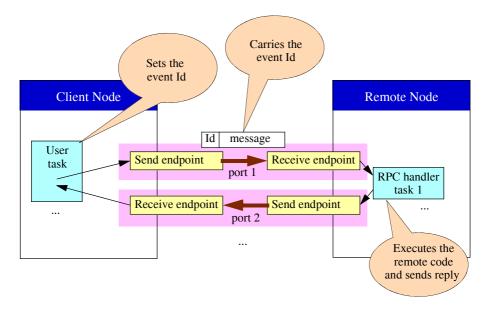

The enhancements to the Ada tasking model included in the new Ada 2005 standard [10, Annex D] enable a new approach to hierarchical scheduling in which the global and local schedulers are integrated in a single framework. The new standard keeps fixed priority pre-emptive scheduling (FPPS) as the basic scheduling mechanism, but it defines a set of new features that extend the Ada tasking model in some significant directions:

Fig. 3. Priority band architecture

New dispatching policies. In addition to FIFO within priorities, the new standard includes non pre-emptive FIFO, round-robin, and earliest-deadline first (EDF) dispatching.

The nice properties of the ceiling locking policy for protected object access are preserved when using the new dispatching policies (including EDF) by redefining it in such a way that it is equivalent to the *stack resource* protocol [11].

- Mixed dispatching policies. The new pragma Priority\_Specific\_Dispatching enables different task dispatching policies to be used within a range of priorities. Again, the new definition of the ceiling locking policy ensures bounded priority inversion even when protected objects are used by tasks running under different dispatching policies.

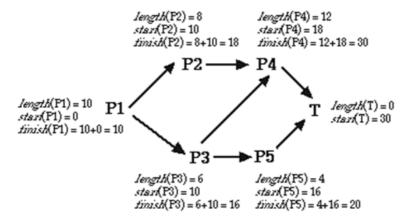

This tasking model suggests an integrated hierarchical architecture in which partitions are implemented as sets of tasks that are assigned priorities within a priority band. The global scheduling policy is FPPS, and the local scheduling policy is the task dispatching policy used in the priority bands assigned to the different partitions (cf. figure 3). This has the advantage of a greater simplicity and flexibility with respect to the server-based architecture.

#### Example 1.1. Sporadic task pattern

```

task body Event_Handler is

-- declarations, including D of type Data

Minimum_Separation : constant Ada.Real_Time.Time_Span

:= ... -- some appropriate value

Next : Ada.Real_Time.Time;

begin

-- Initialization code

loop

Event_Object.Wait(D);

Next := Ada.Real_Time.Clock + Minimum_Separation;

-- Non-suspending event handling code

delay until Next;--this ensures minimum temporal separation

end loop;

end Event_Handler;

```

However, relying on scheduling only for temporal isolation between tasks belonging to different logical partitions (and possibly with different criticality levels) is not enough, as some scheduling-related assumptions might be violated at run-time. The main sources of timing errors are:

- Violations of the arrival models of sporadic tasks (e.g. a sporadic task being activated more often than stipulated).

- Overruns of execution time with respect to the WCET value considered in the off-line feasibility analysis.

Both forms of run-time misbehaviour can result in an overload situation whereby one or more tasks may miss their deadlines, which is clearly unacceptable for high-criticality tasks. However, Ada 2005 provides some mechanisms which can be used to detect overload situations at run time and react to them in an appropriate way:

- Minimum inter-arrival times for sporadic tasks can be enforced, like in Ada 95,

by using a delay until statement. Example 1.1 shows a sporadic task pattern taken from [12] that follows this approach.

- Overruns of budgeted execution time can be detected by using the executiontime timers and group budget timers that have been introduced as novel features in Ada 2005 [10, D14]. Example Example 1.2 illustrates the use of these mechanisms.

Execution-time timers can be used to detect overruns at the task level, while group budget timers can be used to limit the total execution time of a group of tasks. This mechanism can be used to enforce temporal isolation between partitions, as explained in the next section.

#### Example 1.2. Programming example

```

-- Priority bands --

- Band A (FPPS)

pragma Priority Specific Dispatching (FIFO Within Priorities, 18, 32);

- Band B (EDF)

pragma Priority Specific_Dispatching (EDF_Across_Priorities, 3, 17);

— Band C (RR)

pragma Priority_Specific_Dispatching (Round_Robin_Within_Priorities, 1, 2);

Set_Quantum (1, Milliseconds(150));

Set_Quantum (2, Milliseconds (100));

-- Task specifications --

task Task A1

pragma Priority (30); — Set preemption level

end Task A1;

[...]

task Task C5

pragma Priority (1); -- Set preemption level

end Task C5;

— Group budget declarations —

Budget_A : Group_Budget;

Budget_B : Group_Budget;

Budget C : Group_Budget;

— Overrun handler declarations —

Handler_A : Group_Budget_Handler;

Handler_B : Group_Budget_Handler;

Handler_C : Group_Budget_Handler;

Set Handler (Budget A, Handler A);

Set Handler (Budget B, Handler B);

Set Handler (Budget C, Handler C);

— Attach tasks to groups —

Add_Task (Budget_A, Task_A1);

Add_Task (Budget_A, Task_A2);

[...]

Add Task (Budget C, Task C5);

-- Sample protected objects --

\label{eq:protected} \textbf{protected} \ \ \textbf{B}\_\textbf{To}\_\textbf{A}\_\textbf{Flow}\,;

— Set preemption level

pragma Priority (25);

procedure Check And Read Data (...);

entry Write Data (...);

private

end B To A Flow;

```

#### 3.2 Mapping Partitions to Ada 2005

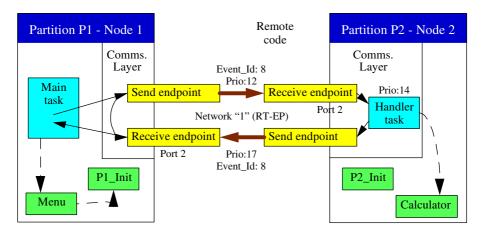

The above approach can be used to map a system with several applications, possibly with different criticality levels, to a set of Ada 2005 tasks with interpartition temporal isolation.

The main architectural rule is to allocate a priority band to every logical partition. The priority band for a partition should contain as many different priority levels as tasks in the partition, so that each task can have a distinct base priority if required. We assume that task priorities are static, except for priority inheritance under the ceiling locking protocol.

The way of assigning priorities to partitions should be directly linked to their criticality levels, i.e it seems reasonable that the partitions with the higher criticality levels are allocated higher priority bands than lower criticality ones. In this way, if an overrun occurs, tasks belonging to low-criticality partitions will miss their deadlines before tasks in higher criticality partitions do. Of course, this priority assignment is not optimal, in contrast with other well-known priority assignment methods [13, 14, 15]. This sub-optimality means that the achievable processor utilization may be inferior to what could be attained with an optimal priority allocation. In practical developments however the theoretical utilization limits attained by the optimal methods are seldom sought and reached.

Communication between tasks in the same partition is mediated by protected objects in the usual style. Inter-partition communication can also be realized with protected objects, but in that case the ceiling priority of the protected object used for it will always be in the priority band of the highest priority partition. This ensures that the criticality level of the latter is also preserved when executing protected operations. If any partition uses the EDF policy, the stack resource protocol (SRP) ensures a minimal amount of blocking for the highest criticality task too.

Temporal isolation is attained by design, confirmed by temporal analysis, and preserved by execution-time timers at run time. A group budget is allocated to each partition, and all tasks in the partition are added to the group. If the budget is exhausted, a handler procedure is invoked to take corrective actions, which in general are application-specific.

The main advantage of the priority bands architecture is the great flexibility it offers to the designer. Contrary to the statically partitioned architecture, modifying the system is comparatively inexpensive, while communications between partitions can be much more easily accommodated. Besides, the fact that the facilities required for its realization are all included in the Ada 2005 standard eases the development process and increases portability. Response time analysis methods for this approach are discussed in the following section.

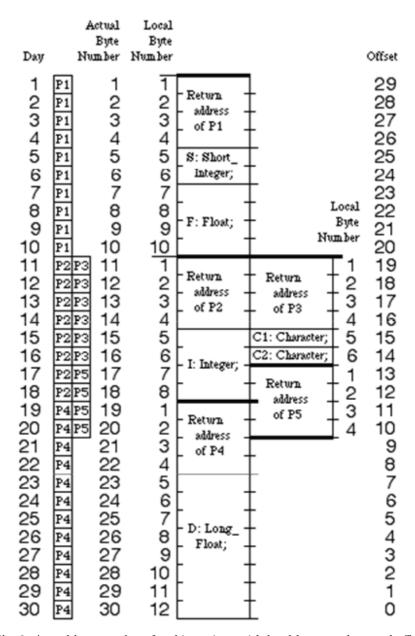

Example 1.2 illustrates a partitioned system containing three applications with three different criticality levels. The scheduling policies are FPPS for level A, EDF for level B, and round-robin for level C. The applications are composed of several tasks which are allocated base priorities within priority bands in accord with their criticality levels. There is a group budget for each priority band, which includes tasks with the same criticality level. Each task group is attached

a handler that is in charge of executing the appropriate code if any of tasks in the group should attempt to execute longer than stipulated.

#### 4 Related Issues

#### 4.1 Response Time Analysis

Temporal analysis is usually required as part of the verification and validation process to be performed in high-integrity systems. The best known temporal analysis methods are usually grouped under the term *Rate-Monotonic Analysis* (RMA) [16] or Response Time Analysis (RTA) [17]. The current form of analysis deals with periodic and sporadic tasks with arbitrary deadlines, precedence relationships, communication through shared data, as well as multiprocessor and distributed systems, using fixed-priority scheduling [18]. Similar results are available for analysing systems based on EDF scheduling [19, 20, 21].

Hierarchical scheduling, on the other hand, is comparatively new, and significant research work has still to be performed to develop or to adapt temporal analysis methods to new scheduling architectures. Some promising results have already been produced [22,6], and especially [23], but their applicability to the proposed scheduling model is still to be explored.

#### 4.2 Spatial Isolation

Although we regard it as outside the scope of this paper, spatial isolation is a mandatory requirement for systems that integrate mixed criticality applications. We are currently exploring two complementary approaches to spatial isolation in systems with hierarchical scheduling. The first one is using SPARK and static flow analysis, as shown in [24], to ensure that non-critical code cannot modify critical data. The other one is based on using specialized hardware mechanisms to enforce isolation between the storage spaces of the different applications at run time, as it is usually done in many operating systems. However, this technique cannot be used in some hardware platforms commonly used in the aerospace domain, that only have rudimentary mechanisms (e.g. fence registers) for memory protection.

#### 5 Conclusions

This paper has illustrated a method for scheduling tasks with mixed criticality requirements. The proposed method can be used to enforce temporal isolation between applications with different levels of criticality. Applications are realised as groups of tasks with prescribed time budgets, which warrant that no single task group may ever overrun into the processor time allocated to another group. Each task group is assigned a band of contiguous priorities, within which specific local dispatching policies can be enforced. This method, which protects logical partitions by advanced use of current scheduling theory, permits to implement

high-integrity systems following an integrated approach and therefore gain a precious extent of design flexibility.

The concrete implementation of the proposed architectural approach is greatly facilitated by the use of new real-time features of the new Ada 2005 standard, and in particular: mixed scheduling policies and group budget timers. We contend that this result is only an initial manifestation of the expressive power provided for by the Ada 2005 standard for the construction of new-generation real-time systems.

#### References

- 1. ISO/IEC: TR 15942:2000 Guide for the use of the Ada programming language in high integrity systems. (2000)

- Vardanega, T.: Development of on-board embedded real-time systems: An engineering approach. Technical Report ESA STR-260, European Space Agency (1999) ISBN 90-9092-334-2.

- 3. ARINC: Avionics Application Software Standard Interface ARINC Specification 653-1. (2003)

- 4. Tokar, J.L.: Space & time partitioning with ARINC 653 and pragma profile. Ada Letters **XXIII** (2003) 52–54. Proceedings of the 12th International Real-Time Ada Workshop (IRTAW 12).

- Dobbing, B.: Building partitioned architectures based on the Ravenscar profile. Ada Lett. XX (2000) 29–31

- 6. Davis, R., Burns, A.: Hierarchical fixed priority pre-emptive scheduling. Technical Report YCS-2005-385, University of York (2005)

- 7. Sha, L., Lehoczky, J., Rajkumar, R.: Solutions for some practical problems in prioritized preemptive scheduling. In: IEEE Real-Time Systems Symposium, IEEE Computer Society Press (1986)

- 8. Strosnider, J., Lehoczky, J., Sha, L.: The deferrable server algorithm for enhanced aperiodic responsiveness in hard real-time environments. IEEE Tr. on Computers 44 (1995)

- 9. Sprunt, B., Sha, L., Lehoczky, J.: Aperiodic task scheduling for hard real-time systems. Real-Time Systems 1 (1989)

- 10. ISO SC22/WG9: Ada Reference Manual. Language and Standard Libraries. Consolidated Standard ISO/IEC 8652:1995(E) with Technical Corrigendum 1 and Amendment 1 (Draft 15). (2005) Available on http://www.adaic.com/standards/rm-amend/html/RM-TTL.html.

- 11. Baker, T.P.: Stack-based scheduling for real time processes. Real-Time Systems  ${\bf 3}$  (1991) 67--99

- Burns, A., Dobbing, B., Vardanega, T.: Guide for the use of the Ada Ravenscar profile in high integrity systems. Technical Report YCS-2003-348, University of York (2003)

- 13. Liu, C., Layland, J.: Scheduling algorithms for multiprogramming in a hard-real-time environment. Journal of the ACM **20** (1973)

- 14. Leung, J., Whitehead, J.: On the complexity of fixed-priority scheduling of periodic real-time tasks. Performance Evaluation 2 (1982)

- 15. Audsley, N., Burns, A., Richardson, M., Tindell, K., Wellings, A.: Applying new scheduling theory to static priority preemptive scheduling. Software Engineering Journal 8 (1993)

- Klein, M.H., Ralya, T., Pollack, B., Obenza, R., González-Harbour, M.: A Practitioner's Handbook for Real-Time Analysis. Guide to Rate Monotonic Analysis for Real-Time Systems. Kluwer Academic Publishers, Boston (1993)

- 17. Audsley, N., Burns, A., Richardson, M., Wellings, A.: Hard real-time scheduling: The deadline-monotonic approach. In Halang, W.A., Ramamrithan, K., eds.: Real Time Programming 1991. Proceedings of the IFAC/IFIP Workshop, Pergamon Press (1992)

- Sha, L., Tarek Abdelzaher, Karl-Erik Årzén, Cervin, A., Baker, T., Alan Burns, Giorgio Buttazzo, Marco Caccamo, John Lehoczky, Mok, A.: Real time scheduling theory: A historical perspective. Real-Time Systems 28 (2004) 101–155

- Baruah, S.K., Rosier, L.E., Howell, R.R.: Algorithms and complexity concerning the preemptive scheduling of periodic, real-time tasks on one processor. Real-Time Syst. 2 (1990) 301–324

- Spuri, M., Buttazzo, G.C.: Efficient aperiodic service under earliest deadline scheduling. In: IEEE Real-Time Systems Symposium. (1994)

- Spuri, M.: Analysis of deadline scheduled real-time systems. Technical Report RR-2772, INRIA, France (1996)

- Shin, I., Lee, I.: Periodic resource model for compositional real-time guarantees.

In: Proceedings of the 24th IEEE Real-Time Systems Symposium. (2003)

- González-Harbour, M., Palencia, J.C.: Response time analysis for tasks scheduled under EDF within fixed priorities. In: Proceedings of the 24th IEEE Real-Time Systems Symposium, Cancún, México (2003)

- Amey, P., Chapman, R., White, N.: Smart certification of mixed criticality systems.

In Vardanega, T., Wellings, A., eds.: Reliable Software Technologies Ada-Europe 2005. Volume 3555 of LNCS., Springer-Verlag (2005) 144–155

# A Comparison of Ada and Real-Time Java<sup>TM</sup> for Safety-Critical Applications

Benjamin M. Brosgol<sup>1</sup> and Andy Wellings<sup>2</sup>

**Abstract.** Ada has long been used for developing safety-critical systems, and the upcoming Ada 2005 language revision extends this support. For various reasons Java has not been a serious choice in this domain. However, recent work based on the Real-Time Specification for Java promises to make Java technology a credible alternative. This paper discusses and compares Ada and the RTSJ with respect to the requirements for safety-critical systems, in particular how they can serve as the basis for subsets that can be used for developing safety-certified software.

#### 1 Introduction

Software is safety-critical if a failure can directly cause loss of human life or have other catastrophic consequences. Correctness needs to be demonstrated with high assurance, and regulatory agencies in safety-critical industries typically require system providers to meet stringent certification requirements, e.g. DO-178B [1] in commercial aviation.

A major factor affecting the development of safety-critical software is the choice of programming language. But there is a dilemma: features with the expressive power to make a system easier to design, implement and maintain — e.g., Object-Oriented Programming — also bring semantic complexity that makes the resulting software harder to certify. This is especially true for features requiring run-time support.

This conflict is resolved in practice by defining language subsets (also known as profiles) that exclude features that might interfere with safety certification. But this still raises several issues. A language may have semantics with intrinsic safety certification problems that cannot be addressed by subsetting, and there is also the difficulty of deciding what should be in the subset, and who (the language designer, the compiler implementor, or the programmer) should make the choices.

In practice there have been a range of approaches. Ada has proved to be a viable basis for safety-critical subsets, as evidenced by SPARK, which emphasizes a particular approach towards demonstrating program correctness, and by various Ada compiler implementations targeted to the safety-critical community. C (and thus C++) are less safe starting points, but the guidelines in MISRA-C [2] intend to avoid C's insecurities and error-prone features. Java, in particular the enhanced platform known as

real-time Java, <sup>1</sup> is currently attracting interest from both the research community and from organizations using Java in systems that have safety-critical requirements.

This paper focuses on Ada<sup>2</sup> and real-time Java, discussing how each can serve as the basis for safety-critical subsets (specifically with respect to the certification issues raised by the DO-178B guidelines).

## 2 DO-178B and Programming Language Issues

DO-178B comprises a set of 66 "guidelines" that apply to the development of software for commercial aircraft systems.<sup>3</sup> The document defines five increasingly stringent levels of criticality, from Level E (lowest) through A (highest). Levels A and B apply to systems whose failure may cause loss of life and are thus considered safety critical.

DO-178B's emphasis is on ensuring the soundness of the process used to build the software, as opposed to directly showing that the resulting software product is correct. Compliance with DO-178B involves the preparation of many certification artifacts (generally documentation of various kinds), adherence to configuration management and quality assurance procedures, and a focus on testing.

#### 2.1 General Requirements

With its emphasis on process, DO-178B says very little about the programming language that is to be used. The document likewise says very little about specific features. Nevertheless, from those guidelines that relate to the software verification process it is possible to infer four main requirements that must be met by a language (or language subset) that is used for developing software for systems at levels A or B:

**Reliability.** The language should encourage the development of readable, reliable software (no "traps and pitfalls"). This means early error detection, compile-time checking, intuitive lexical and syntactic properties, and similar sorts of features.

**Predictability.** First, the programmer must be able to know the exact effect of the program's execution. Thus the language semantics needs to be precisely defined — no implementation dependences or undefined behavior. Second, it must be possible to demonstrate statically (before program execution) that time/space constraints will not be exceeded: deadlines are met, and storage is not exhausted or fragmented.

Analyzability. Several DO-178B guidelines deal with code analyzability in connection with testing. For example, requirements- and structure-based coverage analysis must guarantee that all software requirements are implemented and that there is no "dead code" that is present in the system but does not correspond to requirements. Structural coverage analysis is particularly stringent at Level A, for example requiring "modified condition decision coverage" for boolean expressions, and analysis

<sup>&</sup>lt;sup>1</sup> We use the term *real-time Java* to mean the Java platform extended with real-time functionality and predictability, as defined in the Real-Time Specification for Java [3].

<sup>&</sup>lt;sup>2</sup> Unless indicated otherwise, *Ada* in this paper refers to the Ada 2005 language revision currently in progress [4].

<sup>&</sup>lt;sup>3</sup> The guidelines are not specific to aircraft systems and may be used more generally on any system where high confidence in predictability, reliability and safety is required.

at the object code level when there is not direct traceability from source to object. Language features may either help or interfere with performing such analyses.

**Expressiveness.** Safety-critical systems almost always have real-time constraints and deal with hardware interrupts, shared memory, and other low level issues. The programming language (or language subset) needs to support such functionality.

#### 2.2 Language Feature Issues

The requirements just described have tradeoffs, and advances in language technology sometimes complicate compliance with DO-178B.

- **High-Level Features** [*Predictability, Analyzability*]. Programmers use high-level constructs since it saves development time. For example, array slice assignment in Ada is better than writing a loop with element-by-element assignment. However, for the slice assignment the compiler may generate code that contains implicit loops and conditionals. This may be problematic at Level A, for structural coverage at the object-code level. Recursion can simplify some algorithms, at the sacrifice of storage predictability. Subprograms as run-time objects are often useful, but they complicate coverage analysis.

- **Encapsulation** [Analyzability]. The "black box" principle "clients" of a module can access only the module's interface and not its implementation is a basic tenet for robust software design. However, such "information hiding" may be in conflict with the DO-178B guidelines for structural coverage analysis.

- **Object-Oriented Programming.** OOP raises several serious issues with respect to safety certification. especially with respect to traceability. For example:

- Inheritance [Reliability, Analyzability] semantics may lead to several kinds of programming errors: accidental overloading of a method when the intent was to override, or accidental overriding when the intent was to overload or introduce a new method. Inheritance may also exacerbate data coupling (dependence of subclass on fields in superclass) and complicate analysis.

- Polymorphism [Predictability, Analyzability] requires pointers and generally involves dynamic allocation. That raises the issue of memory management / fragmentation / garbage collection. Interface types (as in Java and Ada 2005) complicate analysis since a variable of such a type can reference any object from any class that implements the interface.

- **Dynamic binding** [*Analyzability*] presents serious issues for structural coverage analysis. Unlike a case statement, where the effect (and thus the analysis) is known to be local to the statement itself, a dynamically bound method call may invoke code distant from the context of the call itself.

- **Generics** [Analyzability]. Generics ("templates") are key to successful code reuse, but for safety certification each instantiation must be analyzed individually. Since a generic instance does not directly correspond to source code provided by the developer, generics can be more difficult to certify than the equivalent program with the expanded instance explicit in the source text.

**Inline expansion** [*Predictability*, *Analyzability*]. Inline expansion raises issues similar to generics and also introduces implementation dependences (the compiler may or may not expand invocations inline).

Facilities Requiring Run-Time Support [*Predictability*, *Analyzability*]. Exception handling, concurrency, and memory management require implementation-provided run-time libraries. Even features that are part of the "static semantics" may result in code that was not explicitly provided by the program (for example "type support" routines for assignment and equality). The generality of the language can make certifiability impractical or impossible for such libraries.

The semantics of dynamic features can significantly complicate coverage analysis for application code. With exceptions there may be "catch-all" handler code that is not easily exercised, and throwing an exception may require dynamic allocation. Concurrency features greatly increase the number of control paths in a program and may introduce timing dependences that are difficult to analyze.

Coverage issues likewise arise for the Application Program Interface. Sometimes the largest advantage of a programming language is the set of libraries that accompanies the implementation (math packages, etc.), but if these are not certifiable then they cannot be used in a safety-critical program.

Compiler Optimizations [*Predictability*, *Analyzability*]. In order to improve run-time performance, modern compilers may generate code that is not directly traceable to the source program. Optimization also interacts with exception handling (e.g., if an exception is raised in an expression that has been moved) and concurrency (caching of shared data in thread-local memory). These kinds of issues significantly complicate coverage analysis.

These issues are receiving attention, since there is interest (especially from developers) to use many of these features in safety-critical code, and the impact on certification must be understood by all parties. During recent years several workshops have focused on these topics; one of the results is a 4-volume handbook [5] that analyzes the issues raised by Object-Oriented Technology. The following sections show how Ada and real-time Java address such issues.

## 3 Safety-Critical Support in Ada

Ada addresses the requirements in Section 2.1 by including features that help, and by allowing the program to exclude features that complicate, safety certification.

#### 3.1 Reliability

Ada was designed with an emphasis on reliability, with features such as strong typing, run-time checks, avoidance of error-prone syntax, and many others. For example:

• *Valid attribute*. With this attribute the programmer can check whether a scalar object that is set from an external device has a valid value. This seemingly simple problem was difficult to solve in Ada 83.

- Prevention of dangling references to declared entities. Ada's access type rules prevent creating a "pointer" to a data object or subprogram whose lifetime could be shorter than that of the pointer.

- Specification of intent on operation inheritance. Ada 2005 has syntax that allows the detection (at compile time) of unintended overriding or non-overriding.

- *Task activation control*. Ada 2005 has introduced rules for "atomic" elaboration; this prevents interrupts during package elaboration from invoking handlers that referenced uninitialized data.

- pragma Assert. Ada 2005 has defined a pragma that allows the assertion of a boolean condition, with program control over the effect when the condition is false, for example by raising an exception.

But Ada also has features that can lead to hard-to-detect errors. Providing dynamic allocation but not requiring garbage collection, Ada places storage reclamation responsibilities on the programmer. This entails either unchecked deallocation (risking dangling references) or reusable object pools (requiring careful analysis to use correctly) to avoid storage leakage.

#### 3.2 Predictability

Any language design has to make tradeoffs among deterministic semantics, program efficiency, and implementability across a wide range of processors and operating systems. For example, if an expression can have side effects then order of evaluation is important. But if the language rules dictate order of evaluation, optimizations become more difficult. As another example, if the concurrency features have specific rules for task dispatching, ready queue placement, and the effect of priorities, then the language's implementation on some platforms may be difficult or inefficient. If it lacks such specificity, then a program may have different effects on different platforms.

Ada 95 offered a partial solution to this dilemma by separating the standard into the core language and the specialized needs annexes. For some kinds of features (e.g., tasking) the core language is intentionally permissive, with constraints added in the Systems Programming or Real-Time Annexes.

However, as a compromise, this approach left a number of areas with nondeterministic semantics. The use of various features may result in erroneous execution, bounded errors, or unspecified or implementation-defined behavior. Examples include the effect of reading the value of an uninitialized object, elaboration order choice, and dependence on the parameter passing mechanism (by copy versus by reference).

Beyond the general issue of deterministic semantics, there is also the potential problem of implementation decisions that interfere with a program's time or space predictability. An example is the possibility of implicit use of the heap for unconstrained discriminated records or functions returning unconstrained arrays.

Solving such issues requires one or more of the following:

- Analyzing the program to ensure that the effect does not arise (e.g., no reads of uninitialized data)

- Adhering to a restricted subset that does not contain the feature in question (e.g., avoiding elaboration order nondeterminism by ensuring that all library-level packages can be specified with pragma Pure or Preelaborate)

• Knowing any relevant implementation decisions so that the program effect (including time and space behavior) is deterministic

#### 3.3 Analyzability

Given the size and generality of the full Ada language, arguably the most important feature for safety-critical systems is a pragma that indicates what a program is *not* doing: pragma Restrictions. Indeed, Ada may best be regarded not as a single language but rather as a family of languages. This is important because there is no such thing as *the* safety-critical subset of Ada; instead pragma Restrictions provides a framework that allows a programmer to define the subset needed for his or her application. Sometimes a set of restrictions collectively is useful, and Ada 2005 introduces pragma Profile as a higher level mechanism for this purpose. The now-classic Ravenscar concurrency restrictions [6] are captured in this fashion: pragma Profile (Ravenscar).

An attempt to define a "one size fits all" safety-critical subset is problematic, since the features that need to be restricted depend on the sorts of analyses that will be carried out.<sup>4</sup> This point is discussed and illustrated extensively in [7].

However, the utility of pragma Restrictions depends on how it is supported in practice. An implementation is permitted to "bundle" restrictions, for example by supplying some fixed number of versions of its run-time support libraries. A program that needs some but not all of the facilities in one of these libraries will end up with the entire library, including features that might not be desired. This will require extra expense for certifying software that is not needed (and will also require explanation to the certification authorities as to why such deactivated code is present).

It is much more useful if the implementation is more flexible, supplying run-time support for a feature only if the feature is actually used in the program. This à *la carte* style is provided in some current Ada implementations, for example AdaCore's High Integrity Edition of GNAT Pro.

Ada 95's Safety and Security Annex included several pragmas designed to assist with safety certification-related analysis. In practice most of these pragmas have been too weakly specified to have much of an effect, although Normalize\_Scalars can help in ensuring a deterministic set of initial values.

Ada's exception handling mechanism raises certification issues regarding library complexity and unreachable handler code.

Ada's high-level nature presents specific challenges to analyzability, but again an implementation can allow the user to specify relevant restrictions. For example, since generated code may contain loops or conditionals that were only implicit in the source program, an implementation may allow the user to prevent such code from being generated. (The compiler will either generate alternative code, possibly less efficient, or reject the program if no such alternative is available.) As another example, an implementation may restrict the use of exception handling, e.g. only for "last chance" code that runs before program termination.

<sup>&</sup>lt;sup>4</sup> This is not to argue against the utility of well-defined subsets such as SPARK, but it might be noted that the SPARK subset is derived from a particular approach to program verification. Other approaches could give rise to other subsets.

Unlike other languages, encapsulation in Ada does not conflict with coverage analysis. It is possible to define a test procedure as a child unit, whose body then has full visibility onto the "state" data encapsulated in the specification of private child package.

#### 3.4 Expressibility

Ada provides excellent support for low-level and real-time programming, both of which are typically needed in safety-critical systems. It also is a methodology-neutral language; if OOP is needed then it is available. If OOP is not needed then traditional language features can be used. It is also possible to use Ada 83-style Object-Oriented Design, or Ada 95 tagged types with type extension, but to exclude complicating features such as polymorphism (class-wide types) and dynamic binding

Ada's concurrency model is a good fit for the requirements of safety-critical programming, as is evidenced by the Ravenscar profile.

Ada may be judged weak in the area of distribution and networking, since it lacks many built-in language features or libraries for these domains. However, Ada's Distributed Systems Annex ensures type safety across partitions, and equivalent semantics when partitioning the application. In addition, Ada has extensive standard facilities for interfacing with code in other languages. Thus if there is a certified library available in C, it can be incorporated into an Ada application.

Other Ada limitations include the absence of built-in constructs or library support for common idioms such as periodic tasks. The language also lacks a general annotation facility; SPARK, for example, uses specially interpreted comments.

#### 3.5 Summary

Ada in its entirety is too large a language for safety critical systems, but subsetting is allowed and indeed facilitated by the Restrictions and Profile pragmas. It is strong in terms of underlying reliability features, expressibility, and its flexibility in subsetting. It has a proven track record in the safety arena and in several areas has advanced the state of the art: SPARK, which has demonstrated the practicality of applying rigorous methods to demonstrate correctness of large systems; Ravenscar, which has shown that concurrency features can be used in safety-critical code.

Ada's main potential drawback is with respect to portability in the context of certification. Although Ada in general supports portability well, a program with restrictions that allow certification in one implementation might not be certifiable in another. This is due both to Ada's flexible approach to subsets and to its various semantic implementation dependences. This may be an issue more in theory than in practice, since certification details tend to be rather implementation specific even for language features that are portable.

# 4 Safety-Critical Support in Java

Java [8] was certainly not designed for safety-critical programming, but it is still useful to assess the language as a whole with respect to the requirements in Section 2.1. This will identify problems that must be addressed in a safety-critical subset and will also point to intrinsic issues that will arise in subsets as well as the full language.

#### 4.1 Reliability

Java was designed in response to known insecurities in C and C++ and has many features that support reliable programming. However, it also has some shortcomings. Its primitive numeric types are weakly typed and do not provide a mechanism for defining range constraints. The solution, to define a class with the numeric data as a field, brings run-time overhead (dynamic allocation of new objects) and some notational clumsiness. The signed integer types have "wraparound" semantics on overflow, resulting in the counterintuitive effect that the sum of two positive numbers may be negative. Java carries over the C/C++ syntactic framework almost intact, thereby inheriting a number of programming pitfalls. These include poorly human-engineered numeric literals (what is the value of 0XF00000000000000000, susceptibility to "dangling else" problems, and errors stemming from the use of "=" for assignment. In the OOP area, although Java 1.5 has an annotation, @override, that detects the error of introducing a new or overloaded method when the intent was to override an inherited method, it lacks a facility for addressing the symmetric situation: overriding an inherited method when the intent was to define a new one. Typographical errors or spelling mistakes can result in legal programs with subtle-to-detect bugs. The semantics for class loading can lead to some unexpected effects, with a static field accessed before its explicit initialization value has been assigned. The Java concurrency model is low-level and contains many subtleties (for example with the use of synchronization and the wait / notify mechanism) that can lead to hard-to-detect errors or race conditions. Java allows a function to be invoked as a statement. If this is done unintentionally the program will compile and run but might not give the expected result.

Most of these shortcomings are intrinsic and will apply to subsets as well as to full Java. The thread model problems are somewhat addressable through a combination of an API and a set of restrictions on thread methods (e.g., prohibiting explicit calls on wait and notify). However, the mutual exclusion mechanism – synchronized code and methods – is basic to Java semantics. Since all arrays and class instances are dynamically allocated, "locking" a data structure is more complex in Java (since the data structure may comprise discontiguous parts) than in other languages.

These are not necessarily fatal flaws—it is, after all, possible to certify systems written in C and assembly language. However, their effect is to make the certification process more complex and thus more expensive.

#### 4.2 Predictability

One of Java's strengths is its well-defined semantics, at least for sequential programs. Like Ada, and in contrast to C or C++, Java defines the effect of run-time conditions such as array index out of bounds and storage overflow. But Java goes much further. Decisions that are implementation dependent or unspecified in other languages—such as order of evaluation in expressions, the effect of referencing uninitialized data, the interaction between optimizations (code motion) and exceptions—are specified deterministically in Java.

However, some issues still arise. One is the effect of finalization. Java allows the user to override the finalize method for a new class; during garbage collection for

any object of this class, finalize will be invoked. However, there is no guarantee when garbage collection is performed.

The other major area where Java semantics are ill-defined is the thread model. Priorities are not guaranteed to be used for thread dispatching; priority inversions and other anomalies are possible.

Beyond these issues of deterministic semantics, there is also the issue of how the language supports programs whose run-time resources (particularly space and time requirements) must be predictable. In this area Java presents major challenges:

#### • Memory Management

One of the major strengths of Java is its provision of automatic garbage collection. However, the presence of garbage collection does not prevent memory leaks. Moreover, a program may suffer from unexpected GC-induced interruptions that defeat analysis of time predictability.

#### • Real-Time Deadlines

Safety-critical systems generally have real-time constraints, with hard deadlines that must be met. The Java thread model's nondeterminism, and interference from the Garbage Collector, defeat this requirement:

• Java Virtual Machine Issues

Java is different from traditional languages in that its execution platform is generally a software (JVM) environment. This is not essential, and there are Java compilers that generate code for standard hardware processors. However, if a JVM is used, several issues arise. Most significant is the need to certify the JVM itself, a formidable undertaking in view of Java's rich run-time semantics. There is also the problem that some JVM instructions take an unbounded amount of time (e.g. athrow for exception propagation), complicating analysis of time predictability.

#### 4.3 Analyzability

As a modern, highly dynamic, "pure" Object Oriented Language, Java suffers from many of the issues identified in Section 2.2.

There is no Java analog to Ada's pragma Restrictions. Thus subsetting will be decided by individual Java implementations, or perhaps as the result of a Java Community Process effort. In either case there is a potential loss of flexibility with respect to analysis techniques, if the specific subset contains features that are outside the set allowed by a user's analysis approach.

#### 4.4 Expressibility

On the positive side, Java does provide class libraries for functionality such as networking and distribution. However, these libraries would need to be rewritten if they are to be used for safety-critical systems, with careful attention paid to memory management.

Java also supplies annotations (in V1.5), which can be useful for describing statically analyzable properties.

Java is weak with respect to "systems programming" level features. This is alleviated in part by some of the facilities provided by the RTSJ, but it is likely that low-level programming will require native code, which will complicate certification.

A more encompassing issue is that Java is a "pure" Object-Oriented Language. It is possible to program in Java without using the dynamic OO features—for example with all methods static or final—but that would result in a style that is distinctly non-Javalike. This is an intrinsic issue; it will arise for any subset.

#### 4.5 Summary

The fact that full Java is not appropriate for safety-critical programming is no surprise. The question is whether the impediments can be removed by restricting the language features to a "safe subset", by providing a specialized API, or both.

Although there is no equivalent of SPARK for Java, this problem has to some extent been addressed in other contexts, in industries that, while not safety-critical, demand high reliability and security. As one example, a subset of the Java platform for smart cards [9] removes a number of complex features such as multithreading and garbage collection; class loading is also more restrictive. And there has been some work on formally defining Java's syntax and semantics [10].

As the Java language has evolved, features have been added that are useful for safety-critical programming (and that thus might be candidates for inclusion in a safety-critical subset). These include annotations and the assert statement (although, as in Ada, the assert statement raises issues of coverage analysis for exception handling code that is only executed when "impossible" conditions occur).

#### 5 Safety Critical Support in the Real-Time Specification for Java

This section describes how the RTSJ addresses the safety-critical requirements presented in Section 2.1.

#### 5.1 Safety-Critical Issues

The RTSJ was designed to address Java's shortcomings in the real-time area, and not to serve as an API for safety-critical applications. Nonetheless, many features that satisfy real-time goals also support safety-critical development, so it is useful to see how the RTSJ rates against the requirements of Section 2.1.

**Reliability.** The RTSJ inherits Java's semantic underpinnings and has both the advantages and disadvantages of full Java with respect to reliability. Thus most of the Java problems cited in Section 4.1 also arise in the RTSJ. An exception is the thread model; the problems in full Java have been largely solved by the RTSJ.

Predictability. The RTSJ addresses the major predictability issues with Java. It resolves the underspecified semantics of the general Java thread model, and provides a mechanism (scoped and immortal memory) that can serve as an adjunct to or replacement of the garbage collector. A few issues still arise, however. One is the presence of optional features in the RTSJ (for example, the Priority Ceiling Emulation policy for monitor control). Also, some RTSJ aspects are implementation dependent, such as the placement of preempted threads in ready queues.

**Analyzability.** There are obviously features that would be too complicated for certification and that would thus need to be excluded or substantially restricted, such as asynchronous transfer of control, the general scoped memory model, the full mechanism for monitor control policies, and "on line" (run-time) feasibility analysis. On the other hand, a number of RTSJ features are designed to support analyzability, such as the cost and deadline data supplied to various constructors.

**Expressibility.** The RTSJ supports idioms (periodic, aperiodic and sporadic real-time threads and asynchronous event handlers) that will be useful for safety-critical applications. It also adds some classes that help with low-level programming. On the other hand, the "pure" Object-Oriented nature of Java means that expressing traditional (non-OO) functionality may have a style that is awkward. And although Java is rich in support for distributed applications, distribution was outside the scope of the RTSJ.

In summary, the RTSJ has demonstrated the feasibility of solving Java's most substantive predictability challenges — thread issues and garbage collection problems — in a way that makes sense for real-time programs. It is thus reasonable to consider the RTSJ as a starting point for the design of a safety-critical profile.

## 6 Defining a Safety-Critical RTSJ Profile